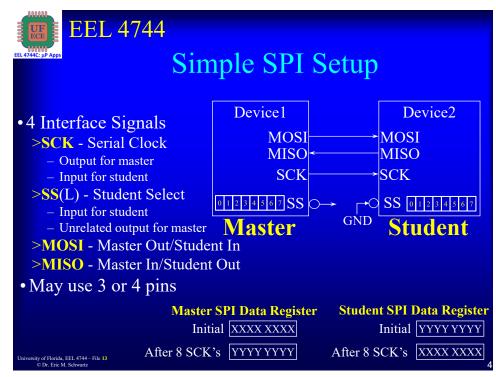

EEL 4744 **XMEGA SPI** • System consists of two shift registers and a master clock generator • Data is shifted out the master's MISO pin • Data is shifted in the master's MOSI pin MSB MASTER LSB MSB SLAVE LSB MISO MISO 8 BIT SHIFT REGISTER 8 BIT SHIFT REGISTER MOS MOS SHIFT ENABLE SPI SCK SCK CLOCK GENERATOR SS SS 6

| EEL 4744<br>SPI Pins on XMEGA<br>• Ports C, D, E, and F each have one SPI<br>> Pins are similar on other ports See doc8385<br>Sec 33.2 Table 33-6. |               |                     |      |      |      |      |      |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|------|------|------|------|------|-----|

|                                                                                                                                                    |               |                     |      |      |      |      |      |     |

| GND                                                                                                                                                | 43            |                     |      |      |      |      |      |     |

| /cc                                                                                                                                                | 44            |                     |      |      |      |      |      |     |

| PF0                                                                                                                                                | 45            | SYNC                | OC0A |      |      |      |      | SDA |

| PF1                                                                                                                                                | 46            | SYNC                | OC0B |      | XCK0 |      |      | SCL |

| PF2                                                                                                                                                | 47            | SYNC/ASYNC          | OC0C |      | RXD0 |      |      |     |

| PF3                                                                                                                                                | 48            | SYNC                | OC0D |      | TXD0 |      |      |     |

| PF4                                                                                                                                                | 49            | SYNC                |      | OC1A |      |      | ss   |     |

| PF5                                                                                                                                                | 50            | SYNC                |      | OC1B |      | XCK1 | MOSI |     |

| PF6                                                                                                                                                | 51            | SYNC                |      |      |      | RXD1 | MISO |     |

| PF7                                                                                                                                                | 52            | SYNC                |      |      |      | TXD1 | SCK  |     |

| niversity of Fl                                                                                                                                    | orida, EEL 47 | 44 - File <b>13</b> |      |      |      |      |      |     |

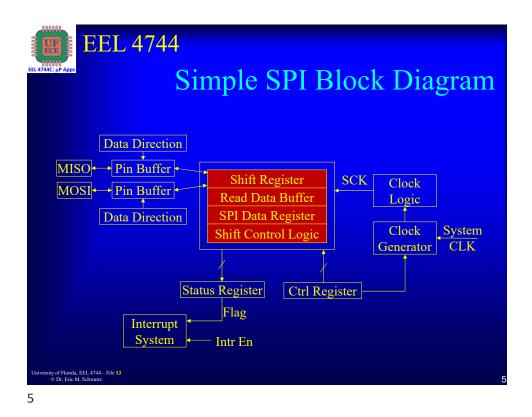

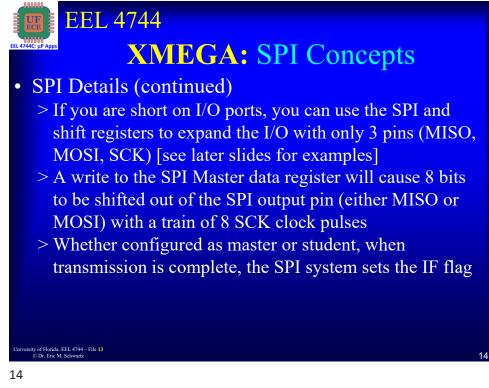

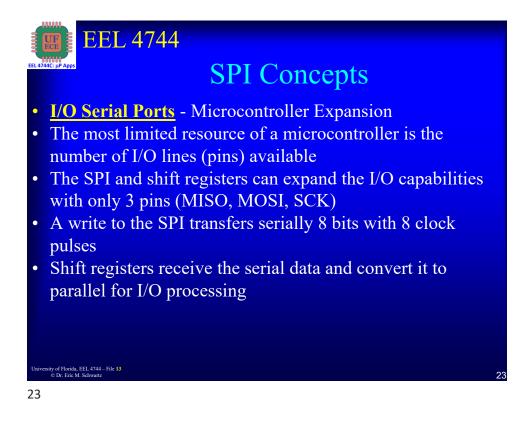

EEL 4744 **XMEGA:** SPI Concepts • SPI Details (continued) > Transmitter is unbuffered and receive is buffered Bytes to be transmitted cannot be written to the SPI DATA register before the entire shift cycle is completed When receiving data, a received character must be read from the DATA register **before** the next character has been completely shifted in (like SCI) > An interrupt can be generated on completion of the transmission/reception of a byte > SCK is an output when configured as a master, an input if configured as student > On both master & student SPIs, the data is shifted on one edge of SCK and sampled on the opposite edge, where the data is stable ty of Florida, EEL 4744 – File 13 © Dr. Eric M. Schwartz 12

University of Florida, EEL 4744 – File 13 © Dr. Eric M. Schwartz

6

9

University of Florida, EEL 4744 – File 13 © Dr. Eric M. Schwartz **SPI**

22

University of Florida, EEL 4744 – File 13 © Dr. Eric M. Schwartz

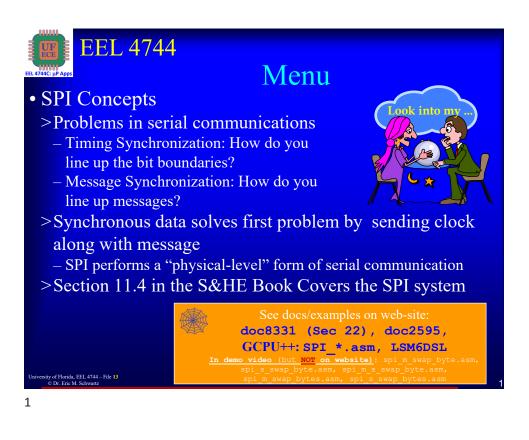

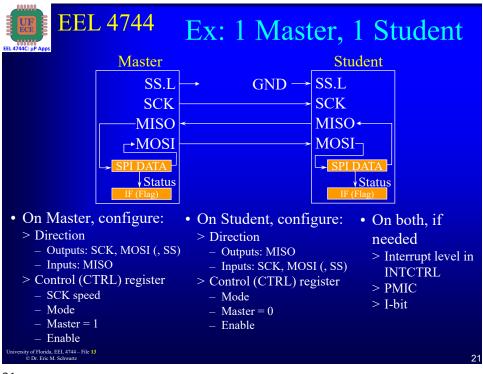

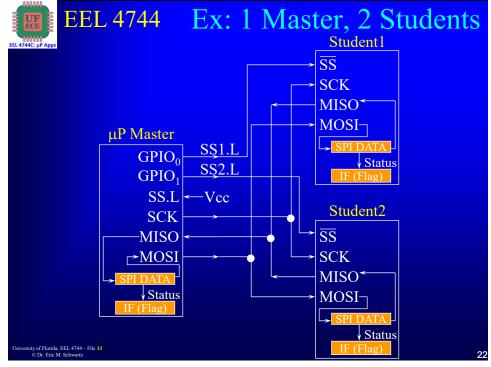

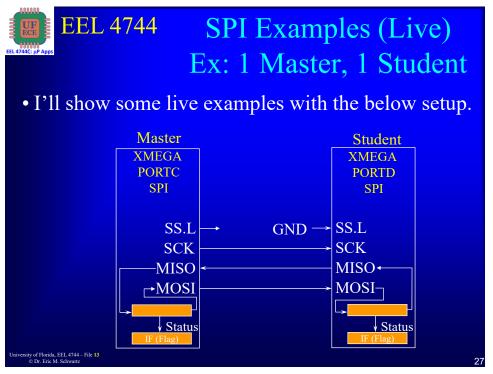

## • Open the following: EEL 4744 SPI Examples (Live) • Copen the following: Ex: 1 Master, 1 Student

- Open the following:

> doc8331, section 22; doc8385, section 33.2

> Include file from Microchip Studio

- Ex1: Setup a master to transmit a single byte and receive a single byte from a student; *SPI\_M\_SWAP\_BYTE.asm*

- Ex2: Setup a student to transmit a single byte and receive a single byte from a master; *SPI S SWAP BYTE.asm*

- Ex3: Setup a master AND student to exchange a byte; SPI\_M\_S\_SWAP\_BYTE.asm

- Ex4: Setup a master to transmit a table of bytes and receive a table of bytes from a student; *SPI\_M\_SWAP\_BYTES.asm*

- Ex5: Setup a student to transmit a table of bytes and receive a table of bytes from a master; *SPI\_S\_SWAP\_BYTES.asm*

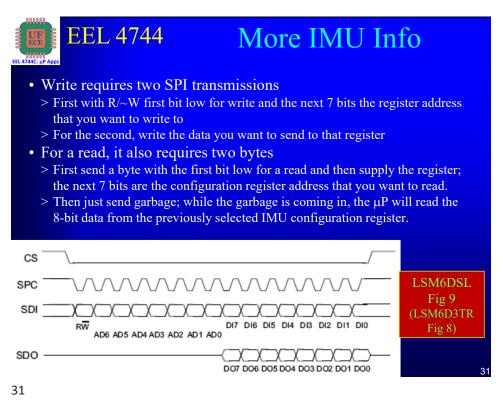

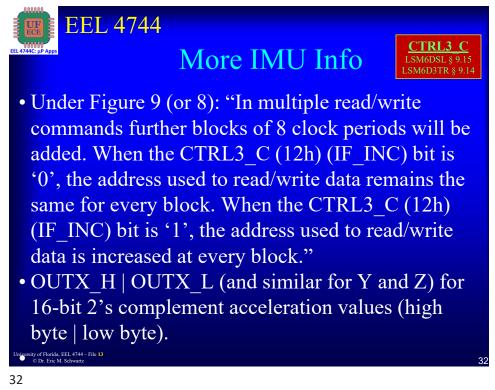

EEL 4744 Lab 6: Interfacing w/ IMU • See Robotics backpack analog (MUXes) switches Master Student for IMU using SPI or I2C (below left) XMEGA IMU > MUX is used to selects which (SPI or I2C) signals are used for SPI IMU (if S is low, SPI used; if S is high I2C); see OOTB Robotics /SS /CS Backpack schematic; (similar for SCK for SPI is Serial CLK) SCK SCK • See IMU document > See Fig 3 (in either LSM6DSL or LSM6DS3TR); compare to XMEGA SPI MISO MISO timing MOSI MOSI CS (chip select), SPC (SPI clock), SDI/SD0 (data input/output) INTR PortC 6 > Read § 6.4 in LSM6DSL [§ 6.2 in LSM6DS3TR] - SPI bus interface - LSM6DSL Fig 9 [8]; compare to XMEGA SPI timing **Analog MUX** In Fig 9, R/~W is the first bit in the address, telling you if MOSI reading or writing to the IMU  $\mathbf{R1}$ Serial IN • SDI (input to IMU): R /W ADR6:ADR0 | DI7:DI0 SDA-**B**2 • SDO (output from IMU): X7:X0 | DO7:DO0 (X not used) > Table 6: SPI clock frequency maximum ~CS/I2C EN > Section 8 – Register mapping WHO\_AM\_I (Read only, at address 0x0F) y of Florida, EEL 4744 – File <mark>13</mark> © Dr. Eric M. Schwartz Value is 0x6A [0x69], for LSM6DSL[for LSMDS3TR]

30